# ADM32F036A3Q 数字信号处理器

数据手册

**ADM32F036A3QN56Q**

Advancechip

**Electronics**

# 湖南进芯电子科技有限公司

2025年3月

V1.0

## 目 次

| 1 产品特征                                        | 1  |

|-----------------------------------------------|----|

| 2 ADM32F036A3Q 简介                             | 2  |

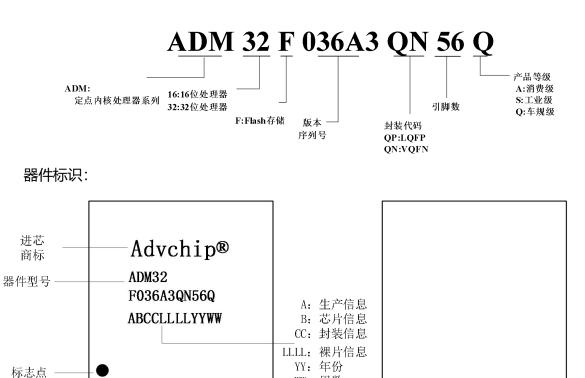

| 2.1 产品编码                                      | 2  |

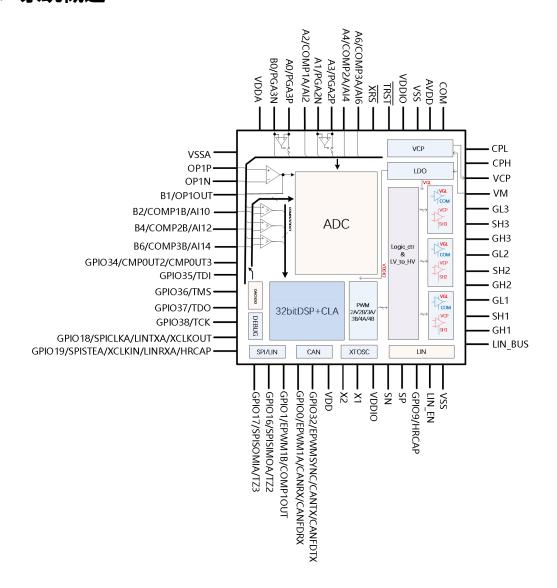

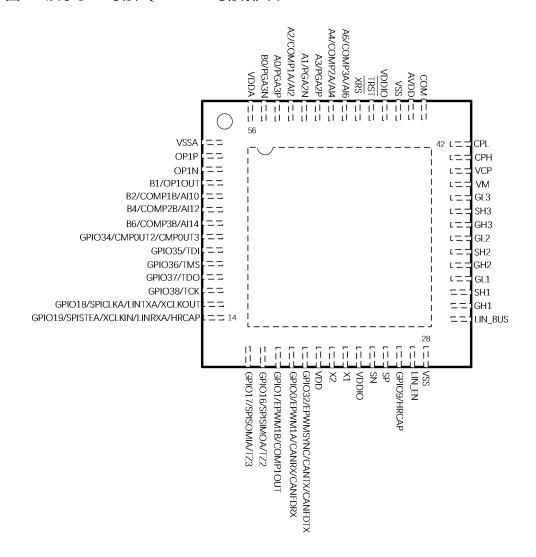

| 2.2 系统概述                                      |    |

| 2.3 引脚排布及说明                                   |    |

| 2.4 引脚定义                                      |    |

| 3 功能概述                                        | 8  |

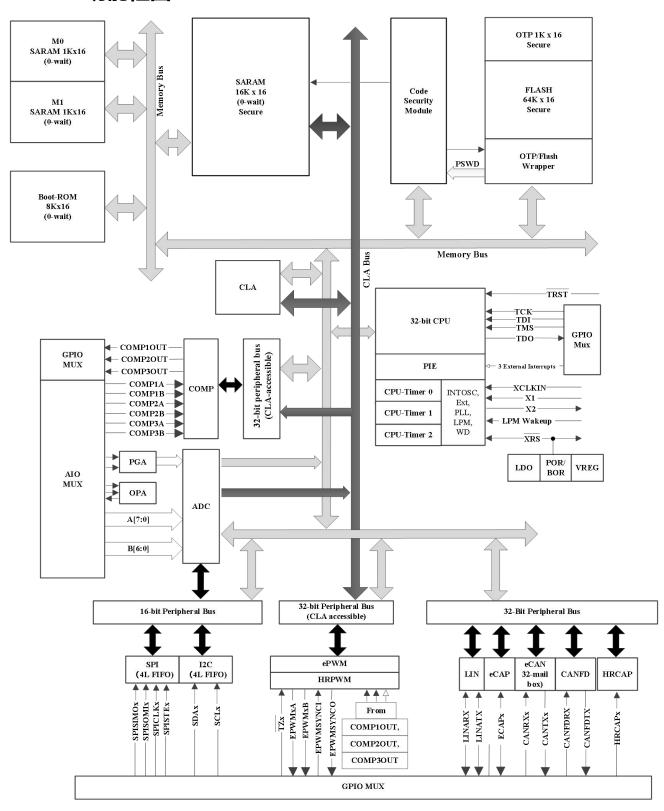

| 3.1 DSP 功能框图                                  | 8  |

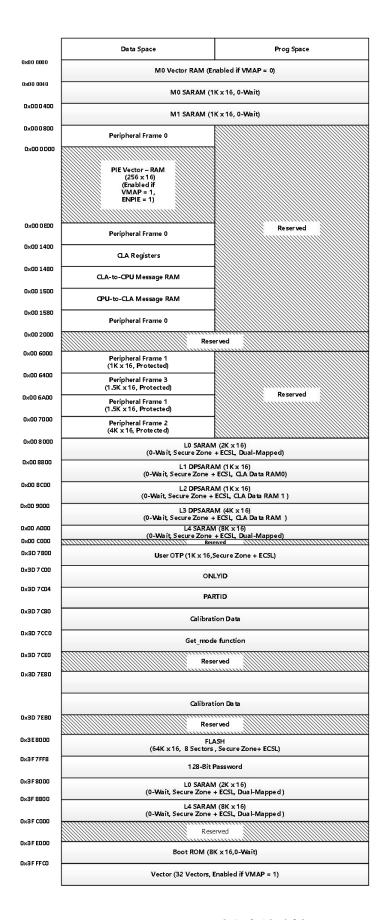

| 3.2 内部存储映射                                    | g  |

| 3.3 简要说明                                      | 13 |

| 3.3.1 ADM32F036A3Q DSP                        | 13 |

| 3.3.2 控制律加速器 (CLA)                            |    |

| 3.3.3 存储总线(哈佛总线架构)                            | 13 |

| 3.3.4 外设总线                                    | 14 |

| 3.3.5 实时 JTAG 和分析                             | 14 |

| 3.3.6 闪存                                      | 14 |

| 3.3.7 M0、M1 SARAM                             | 14 |

| 3.3.8 L0 SARAM、L4 SARAM 和 L1、L2 以及 L3 DPSARAM | 15 |

| 3.3.9 引导 ROM                                  | 15 |

| 3.3.10 器件加密                                   | 17 |

| 3.3.11 SRAM 诊断                                | 18 |

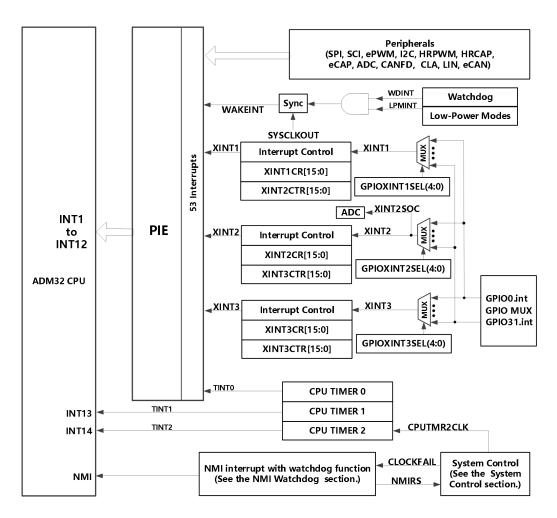

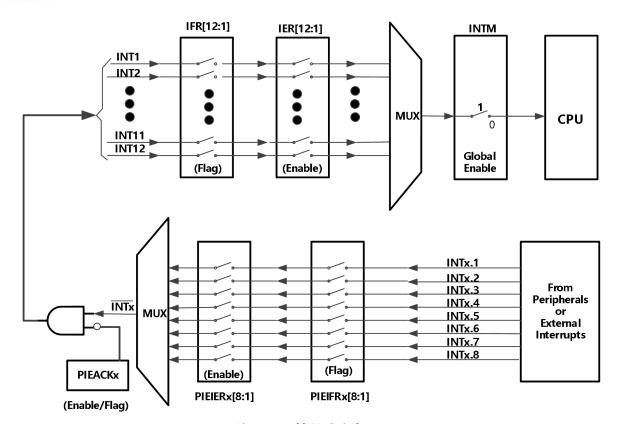

| 3.3.12 外设中断扩展 (PIE) 块                         | 19 |

| 3.3.13 外部中断 (XINT1-XINT3)                     | 19 |

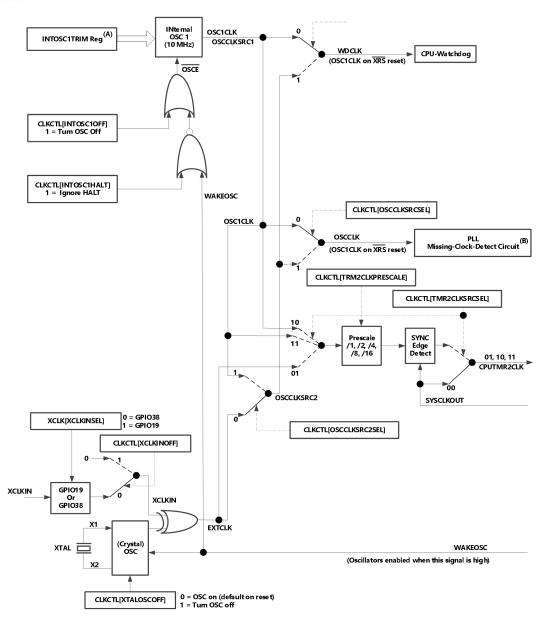

| 3.3.14 内部零引脚振荡器、振荡器和 PLL                      | 19 |

| 3.3.15 看门狗                                    | 19 |

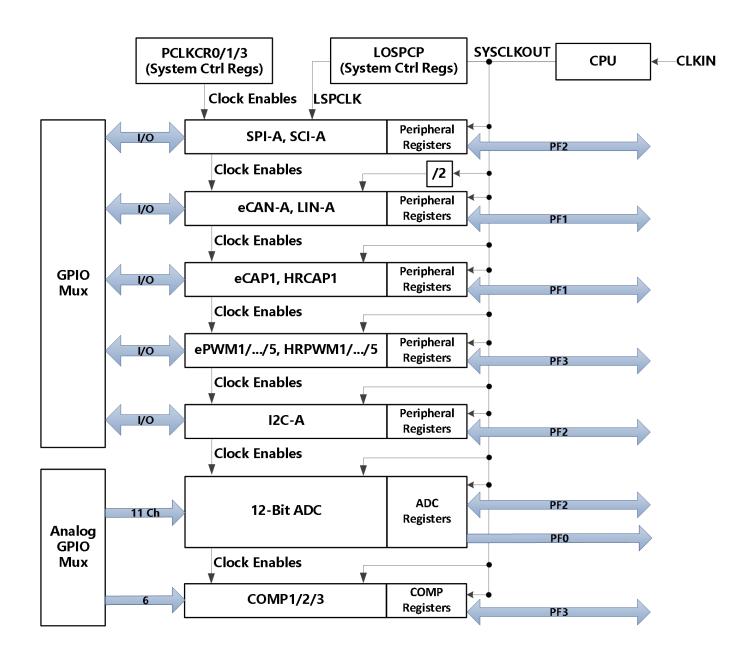

| 3.3.16 外设时钟                                   | 20 |

| 3.3.17 低功耗模式                                  | 20 |

| 3.3.18 外设帧 0,1,2,3 (PFn)                      | 20 |

| 3.3.19 通用输入/输出(GPIO) 复用器                      | 21 |

| 3.3.20 32 位 CPU 定时器 (0,1,2)                   | 21 |

| 3.3.21 控制外设                                   | 22 |

| 3.3.22 串行端口外设                                 | 22 |

| 3.4 寄存器映射                                     | 24 |

| 3.5 仿真寄存器                                     |    |

| 3.6 中断                                        |    |

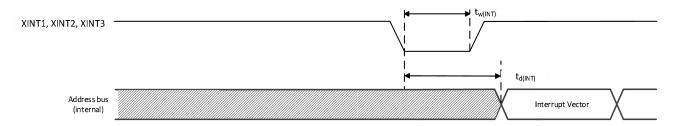

| 3.6.1 外部中断                                    |    |

| 3.6.2 外部中断时序                                  |    |

## ADM32F036A3Q Digital Signal Processor

| 3.7 系统控制                       | 31 |

|--------------------------------|----|

| 3.7.1 内部零引脚振荡器                 | 33 |

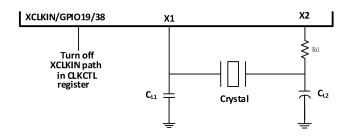

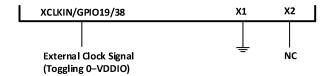

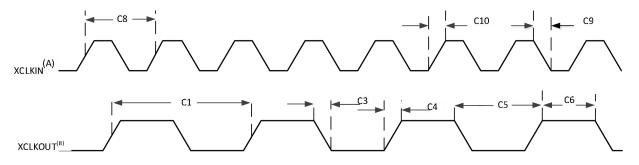

| 3.7.2 晶体振荡器选项                  | 34 |

| 3.7.3 PLL 时钟模块                 | 35 |

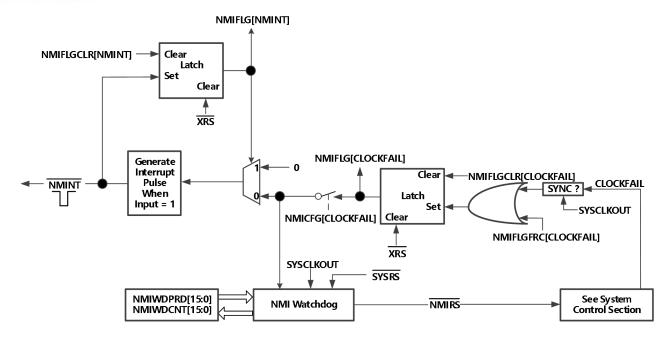

| 3.7.4 输入时钟丢失(NMI 看门狗功能)        | 37 |

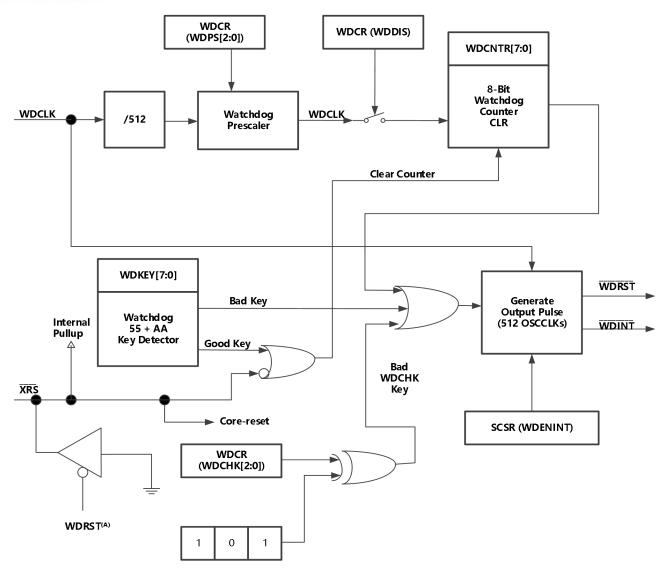

| 3.7.5 CPU 看门狗                  | 38 |

| 3.8 低功耗模式                      | 40 |

| 4 外设                           | 41 |

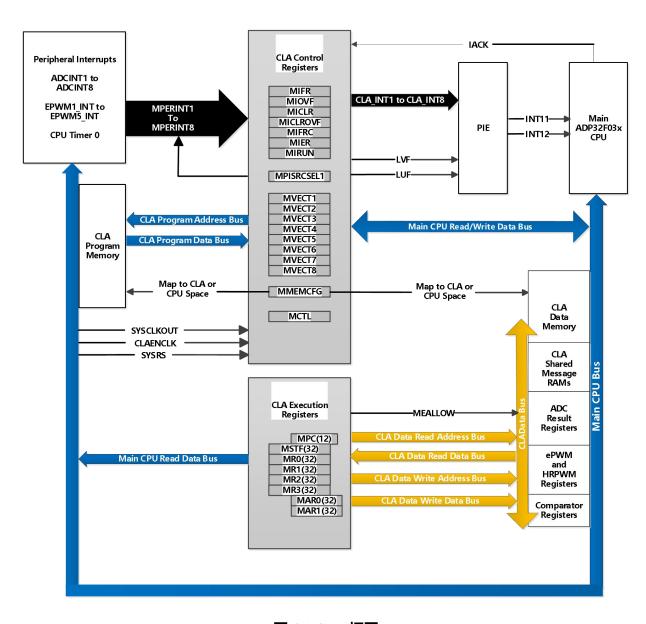

| 4.1 控制律加速器 (CLA)               | 41 |

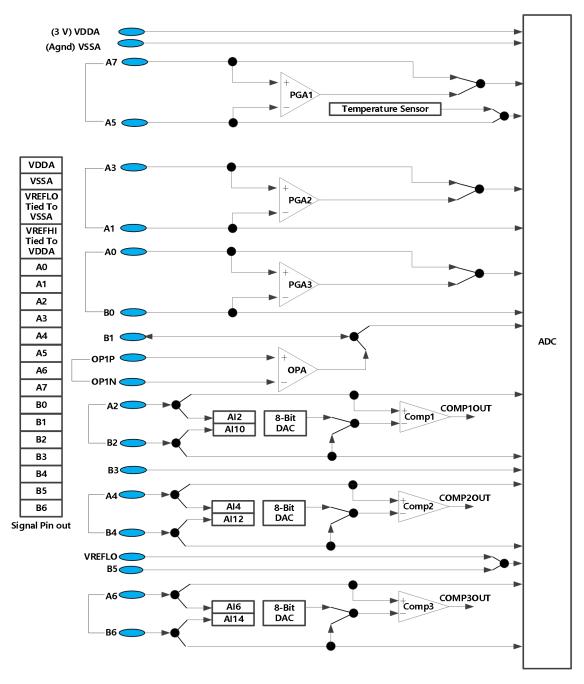

| 4.2 模拟模块                       |    |

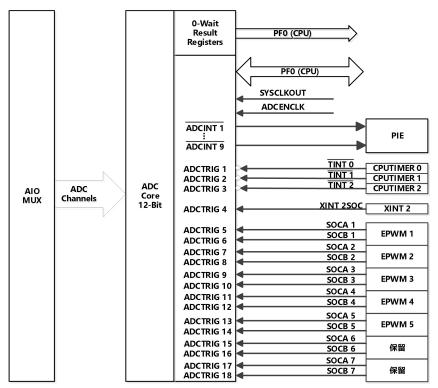

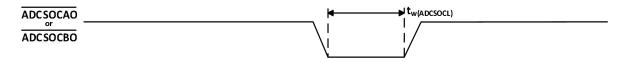

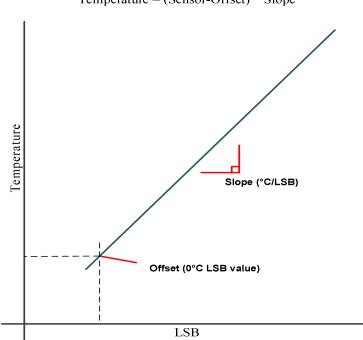

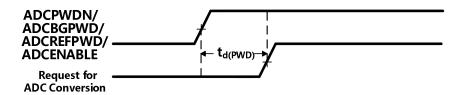

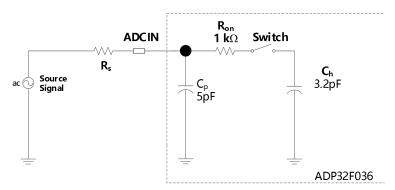

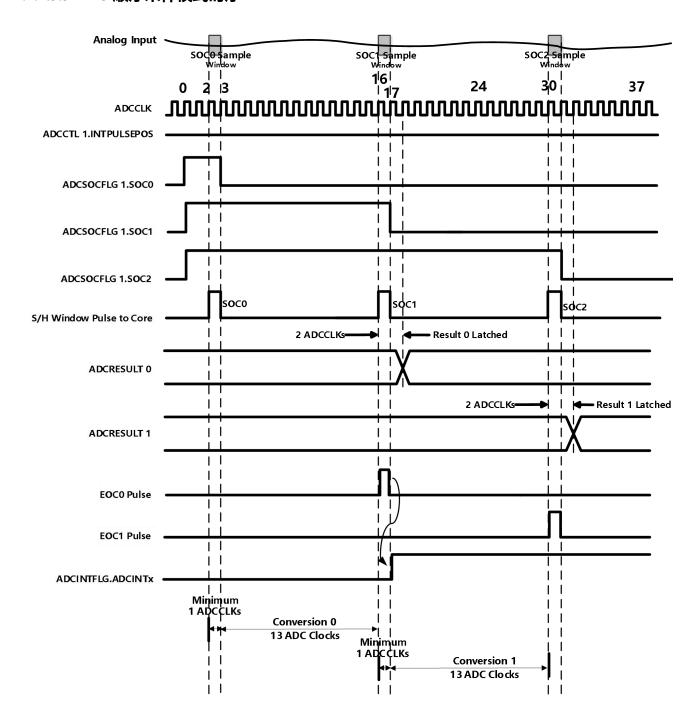

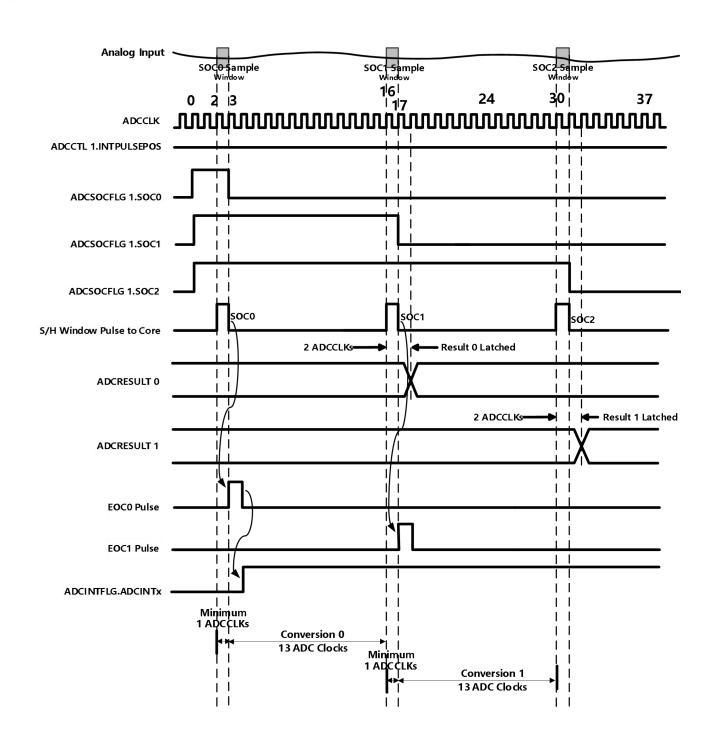

| 4.2.1 ADC                      |    |

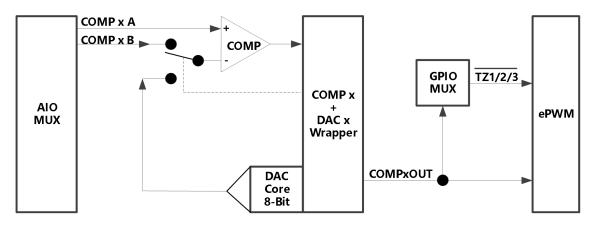

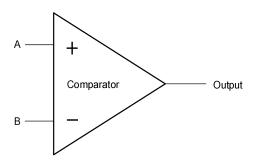

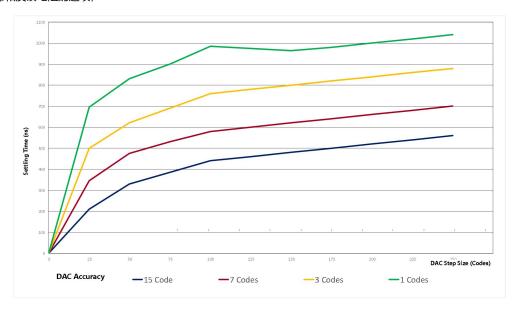

| 4.2.3 比较器模块                    |    |

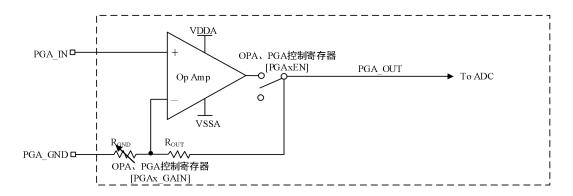

| 4.2.4 可编程增益放大器(PGA)、运算放大器(OPA) |    |

| 4.3 同步串行通信接口 (SPI) 模块          |    |

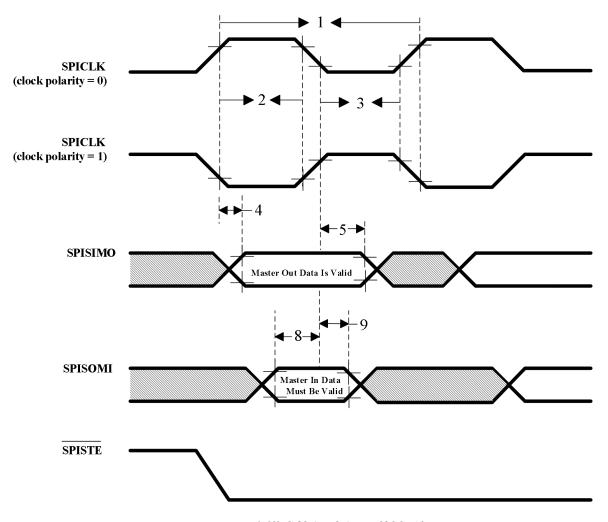

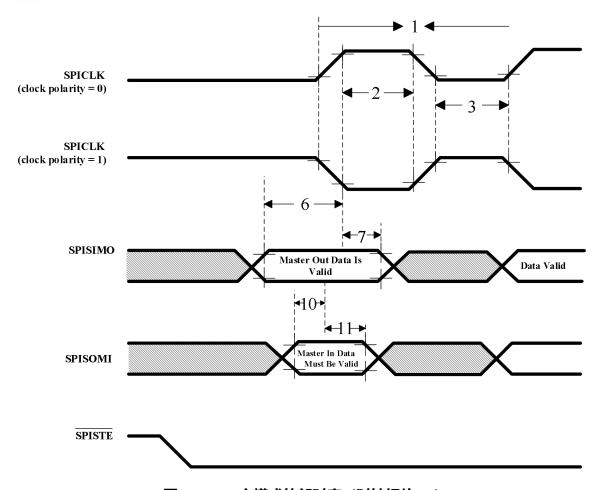

| 4.3.1 同步串行通信接口(SPI) 主模式时序      |    |

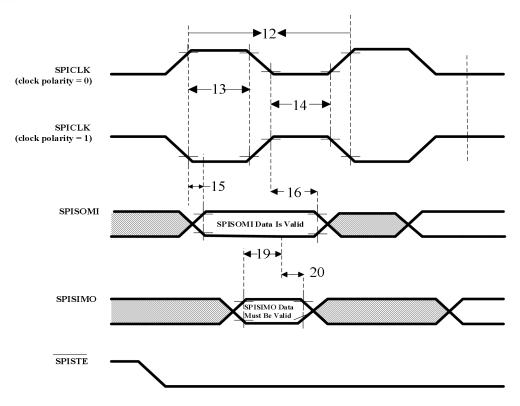

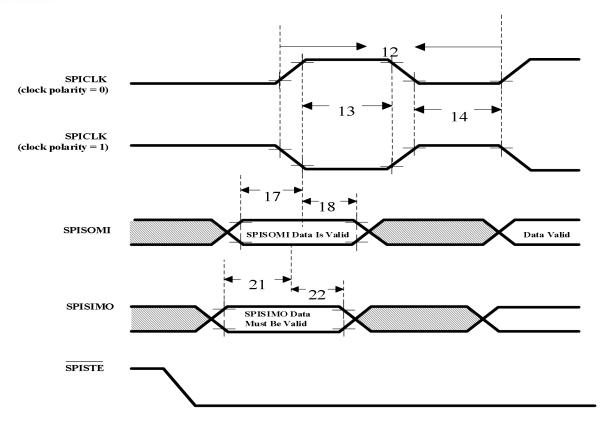

| 4.3.2 SPI 从模式时序                |    |

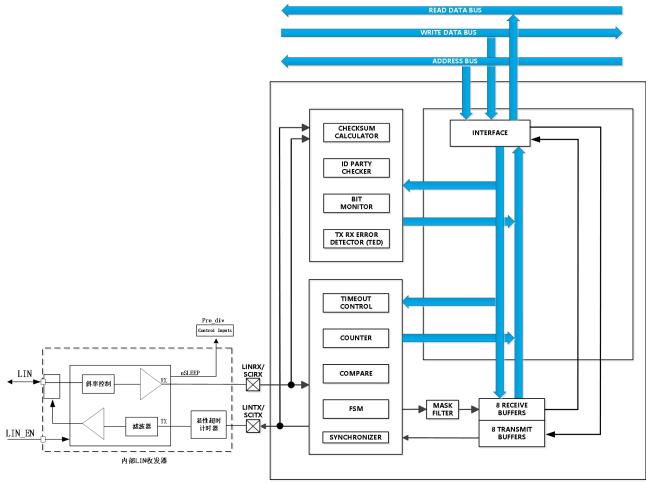

| 4.4 本地互连网络 (LIN)               |    |

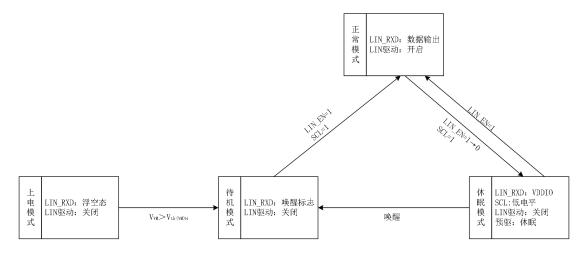

| 4.4.1 工作模式                     |    |

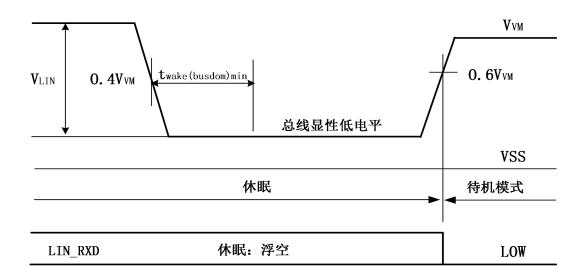

| 4.4.2 远程唤醒                     |    |

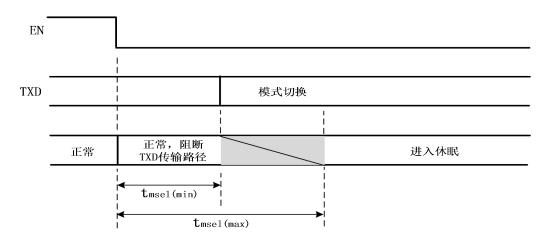

| 4.4.3 显性超时功能                   |    |

| 4.4.4 失效安全特性                   |    |

| 4.4.5 LIN 模块电气特性               |    |

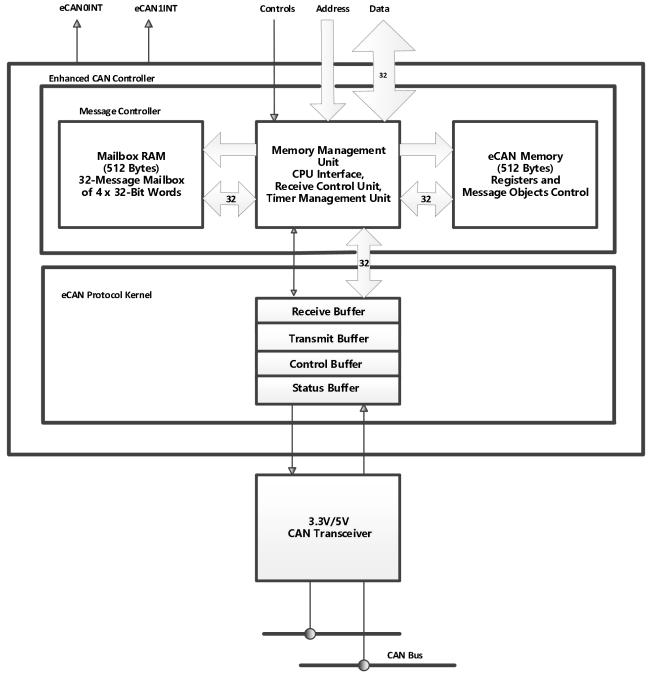

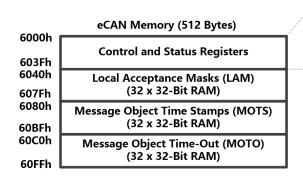

| 4.5 增强型控制器局域网络 (ECAN) 模块       |    |

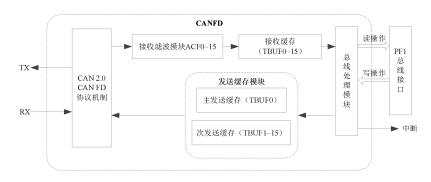

| 4.6 可变速率控制局域网(CANFD)模块         |    |

| 4.6.1 简介                       |    |

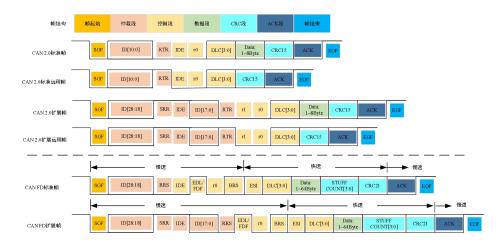

| 4.6.2 CANFD 协议说明               |    |

| 4.6.3 CANFD 模块特性说明             |    |

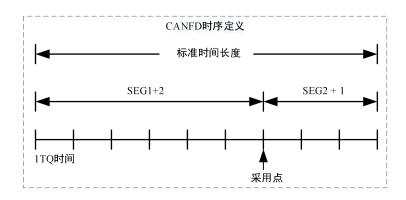

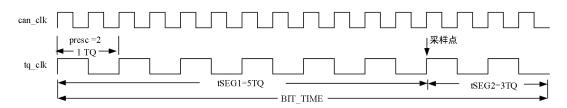

| 4.6.4 时钟配置                     |    |

| 4.6.5 引脚配置                     |    |

| 4.6.6 中断配置                     |    |

| 4.6.7 传输模式                     |    |

| 4.6.8 帧类型                      |    |

| 4.6.9 发送帧                      |    |

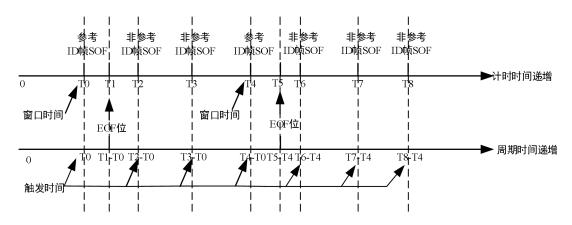

| 4.6.10 CIA603 时间戳              |    |

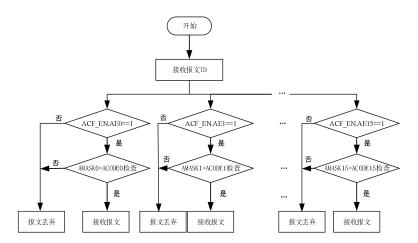

| 4.6.11 接收帧和滤波                  |    |

| 4.6.12 休眠模式                    |    |

| 4.6.13 错误                      |    |

| 4.6.14 寄存器描述                   |    |

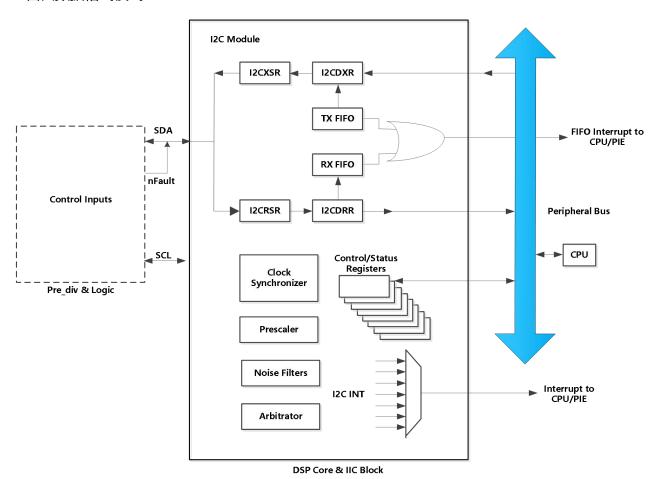

| 4.7 内部串行 IIC 模块                |    |

## ADM32F036A3Q Digital Signal Processor

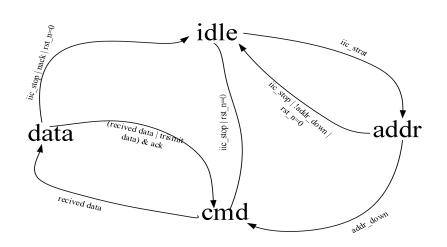

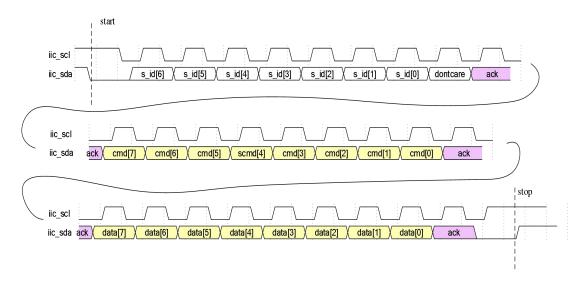

| 4.7.1 IIC 从机功能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 149 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.7.2 寄存器映射                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 151 |

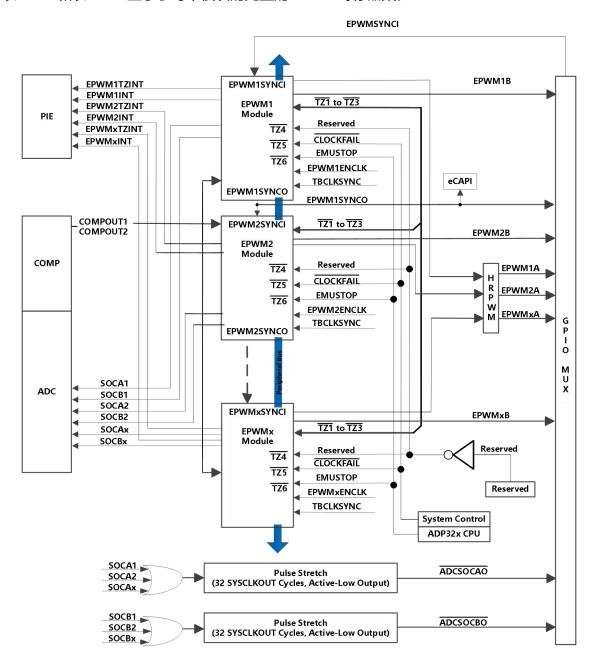

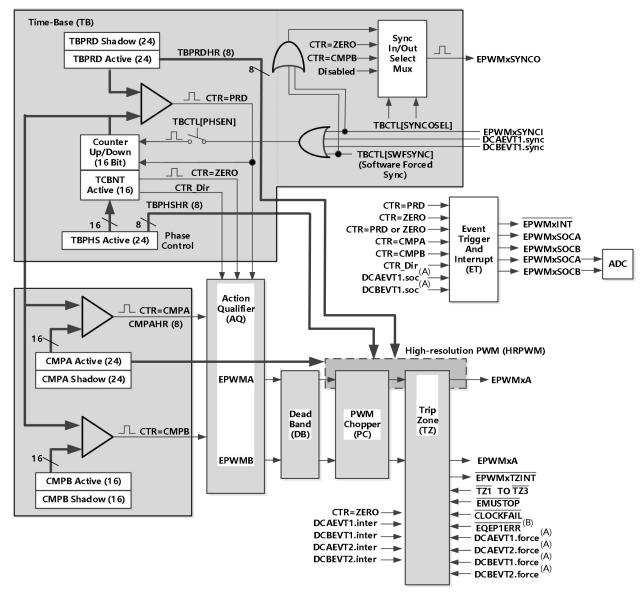

| 4.8 增强型 PWM 模块 (εPWM1/2/3/4/5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 160 |

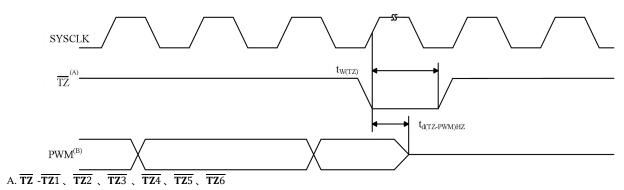

| 4.8.1 增强型脉宽调制器 (ePWM) 时序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 165 |

| 4.8.2 可编程控制故障区输入时序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 165 |

| 4.9 高分辨率 PWM (HRPWM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 166 |

| 4.9.1 高分辨率 PWM (HRPWM) 时序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 166 |

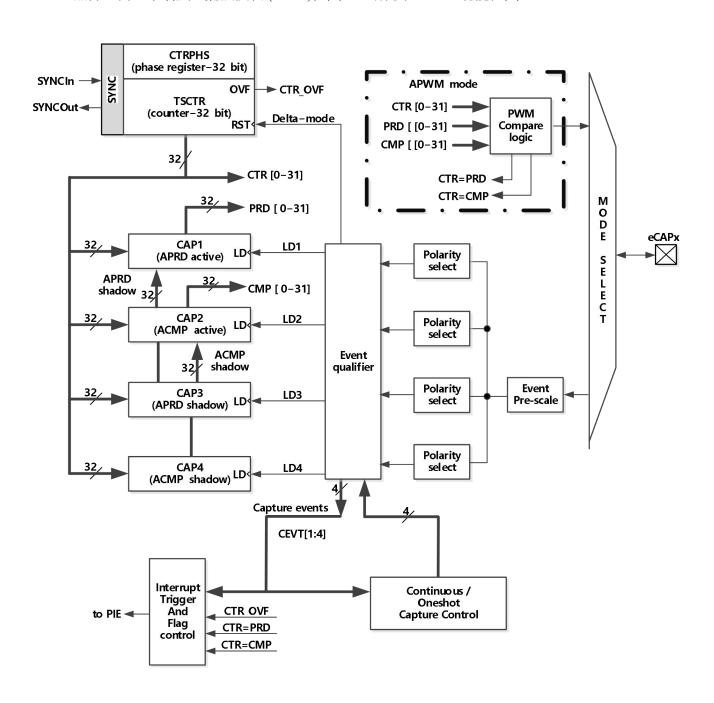

| 4.10 增强型捕获模块 (ECAP1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 167 |

| 4.10.1 增强型捕获 (eCAP) 时序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 168 |

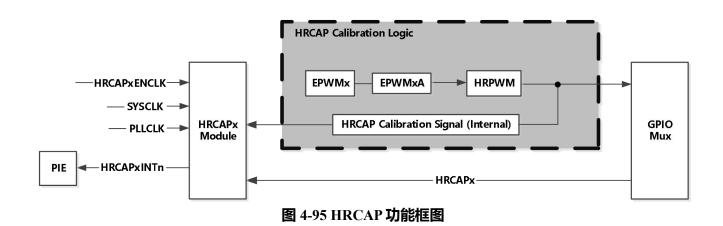

| 4.11 高性能捕获 (HRCAP) 模块                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 169 |

| 4.11.1 高性能捕获(HRCAP) 时序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 170 |

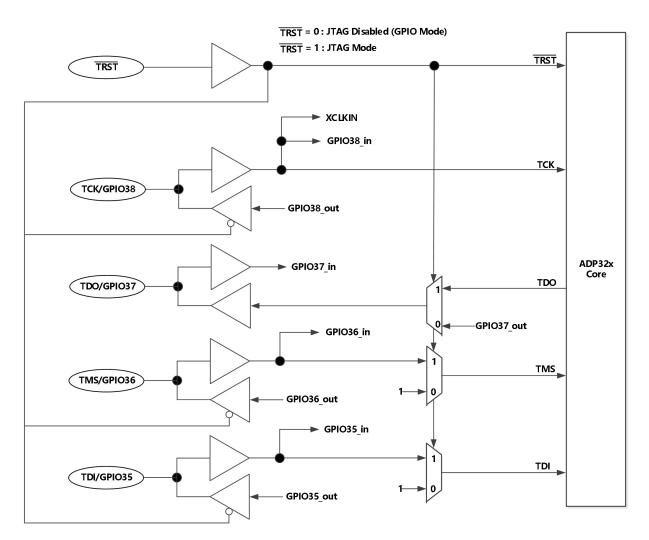

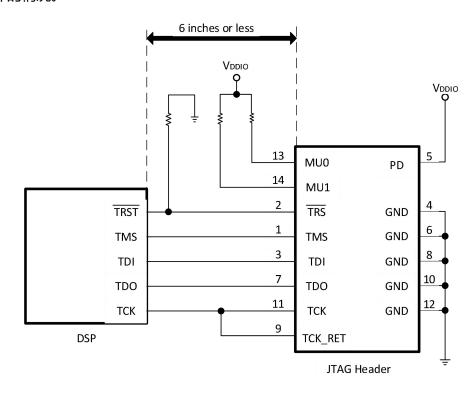

| 4.12 JTAG 端口                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 171 |

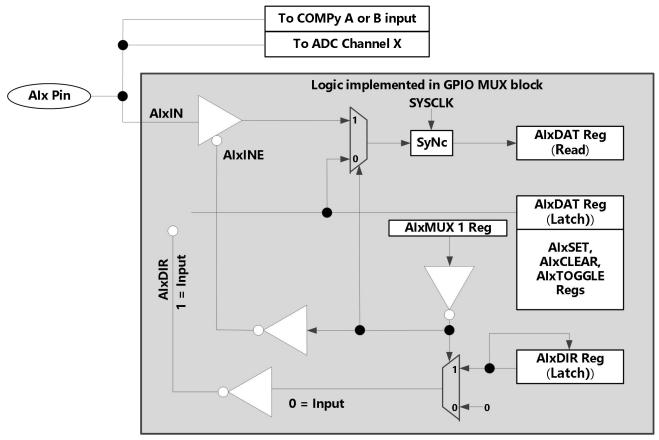

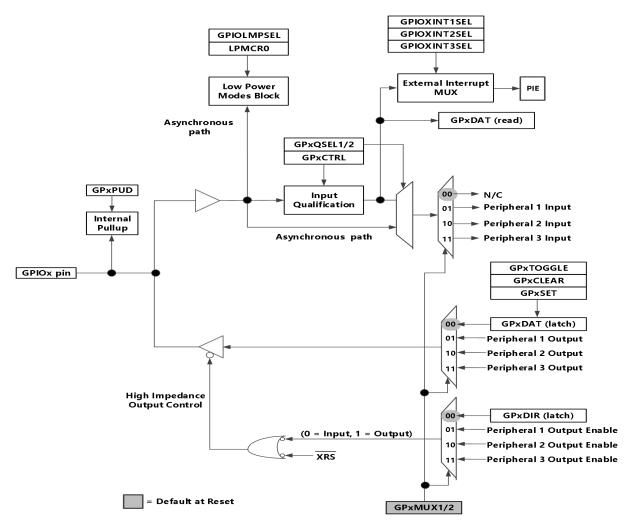

| 4.13 GPIO MUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

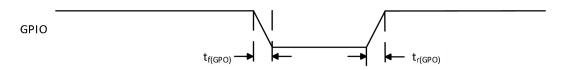

| 4.13.1 GPIO 输出时序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 177 |

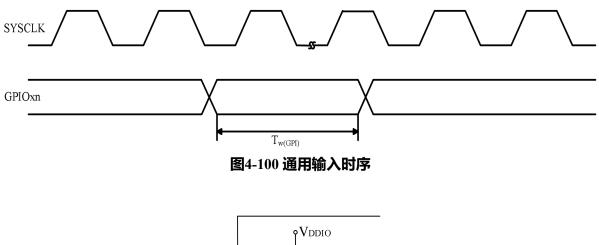

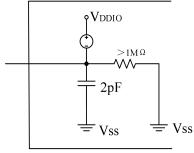

| 4.13.2 GPIO 输入时序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 177 |

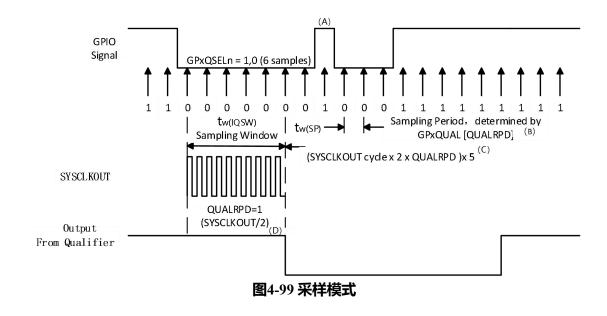

| 4.13.3 输入信号的采样窗口宽度                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 178 |

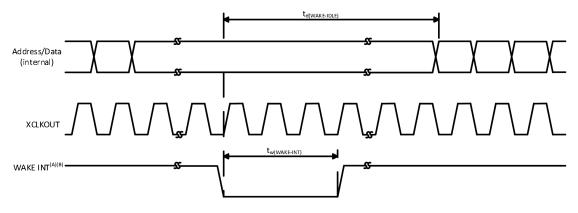

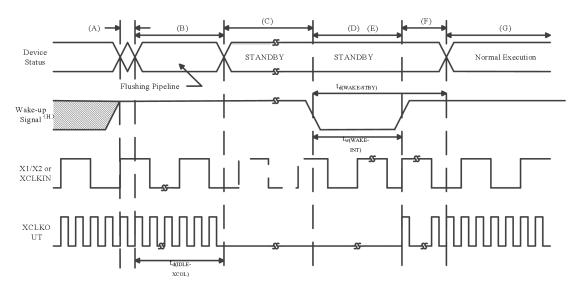

| 4.13.4 低功耗唤醒时序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 179 |

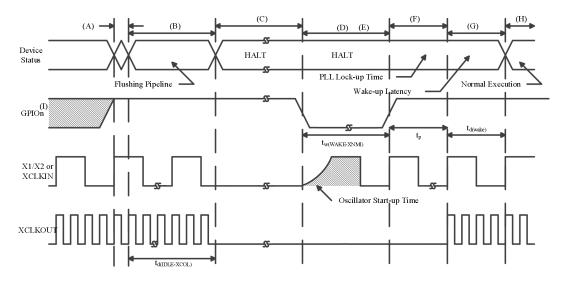

| 5 智能预驱                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 183 |

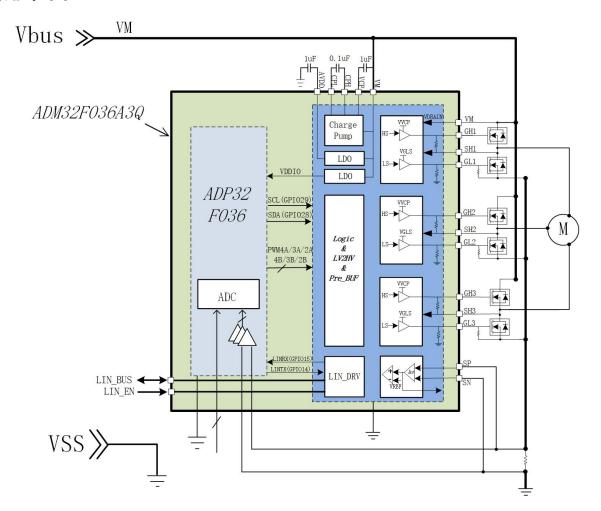

| 5.1 功能框图                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 183 |

| 5.2 概述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 183 |

| 5.3 功能描述                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 5.3.1 母线电流过流保护                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 184 |

| 5.3.2 故障监测与 IIC 通信                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 184 |

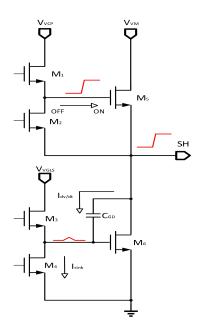

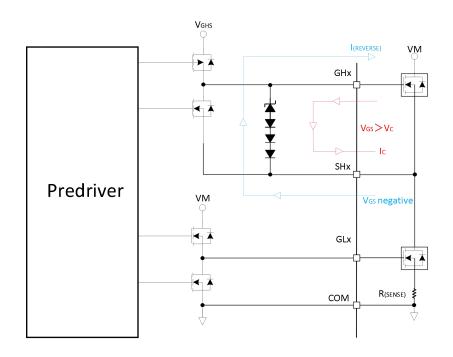

| 5.3.3 PWM 栅极驱动                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 184 |

| 5.3.4 死区时间                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 187 |

| 5.3.5 传输延迟                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 187 |

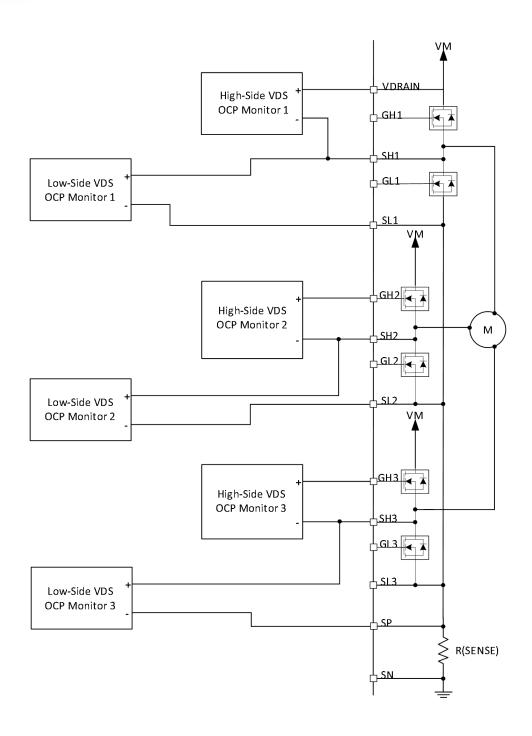

| 5.3.6 VDS 过流检测                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 187 |

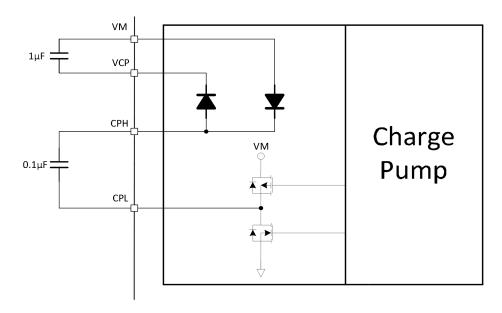

| 5.3.7 电荷泵                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 5.3.8 栅极驱动钳位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 189 |

| 5.3.9 保护电路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 190 |

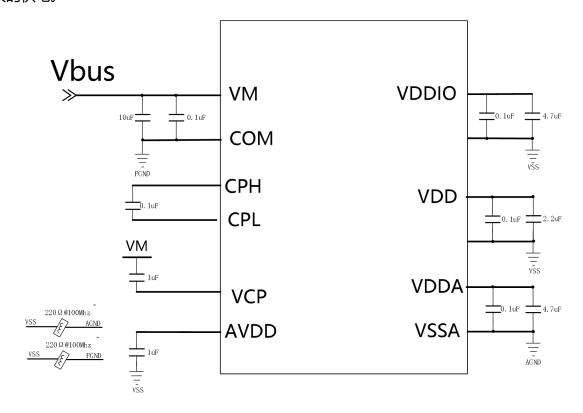

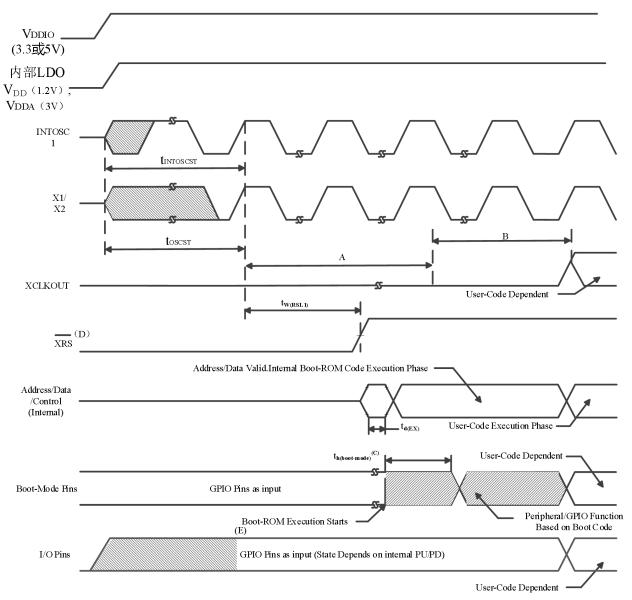

| 6 供电介绍                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 191 |

| 6.1 片上 LDO 电源管理                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 191 |

| 6.2 内核 LDO /BOR/POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 192 |

| 6.2.1 片载电压稳压器 (LDO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 192 |

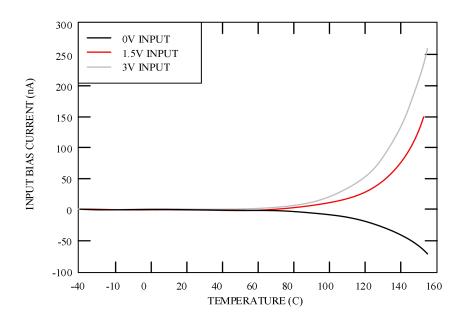

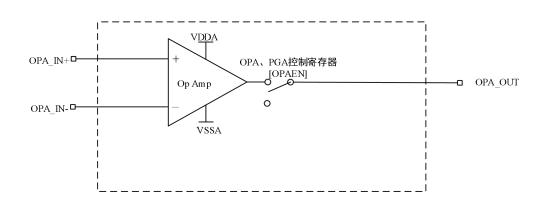

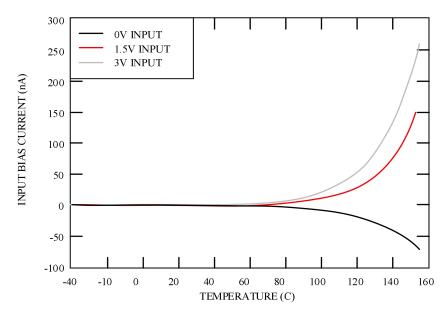

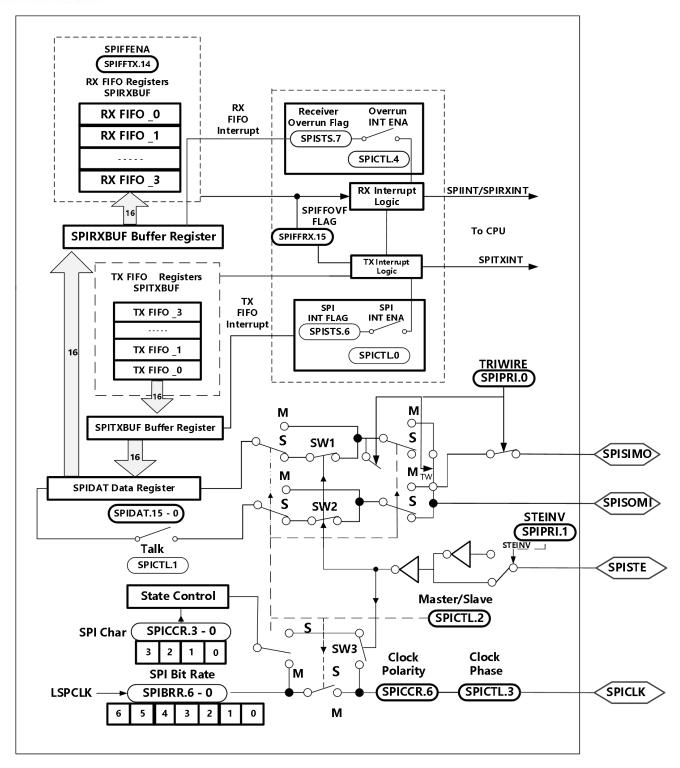

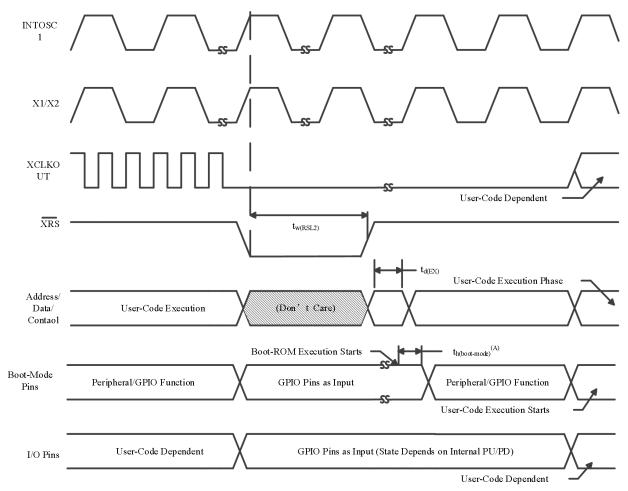

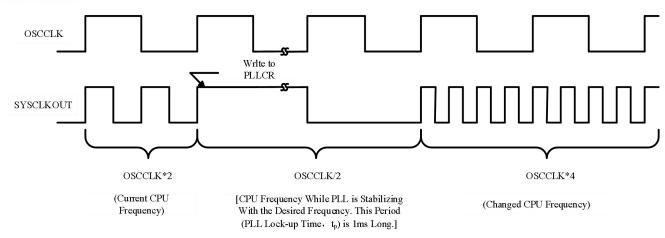

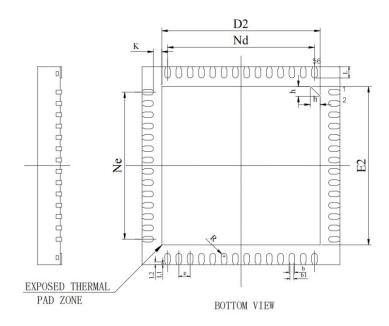

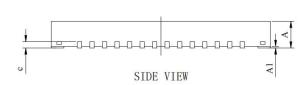

| 6.2.1.1 使用片载 LDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |